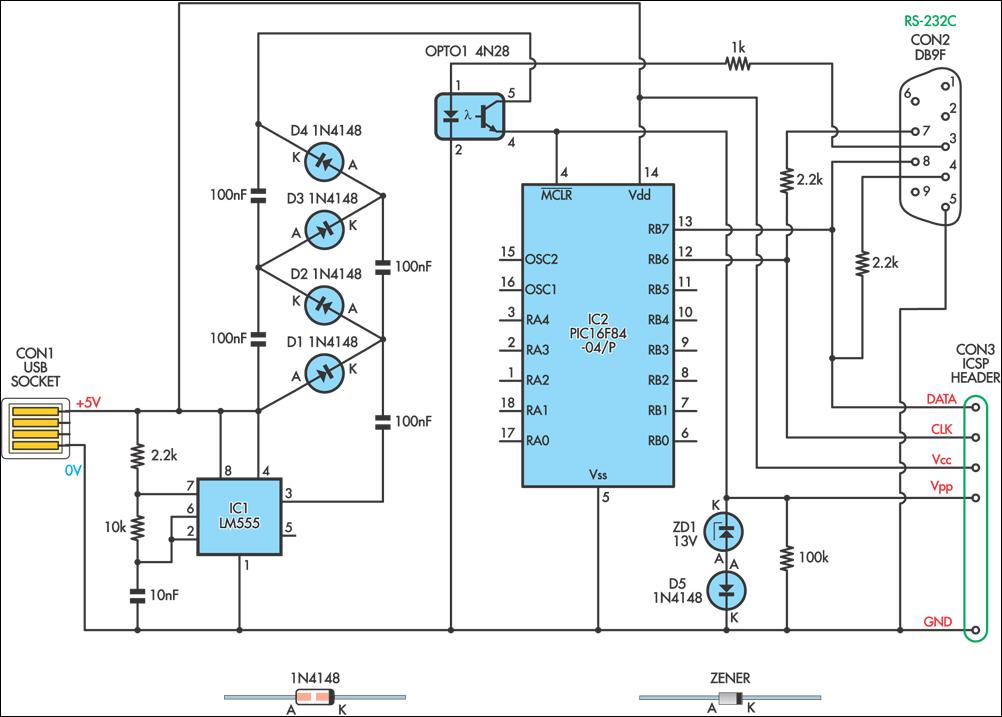

Data for all the devices clocks through all the devices in a chain similar to boundary scan, each device just picks out the data addressed to them.

The MISO of one slave goes to the MOSI of another, chaining them together. Daisy-chain topology splits the clock to route in parallel to the slaves. SPI supports two multi-device topologies, daisy-chain and star. This is transparent to SPI protocol, and enables long-distance and isolated connections. Point-to-point topology allows implementation of transceivers to convert SPI signalling to RS485, or CAN, or fiber-optic, etc.25-50 Mbits/sec data transfers are achievable.The bus can be driven as fast as your chips and board design can handle. Driven by the master to select an individual slave device. Data driven from the slave devices to the master.ĬS_L – Chip Select (Active-Low). Isn’t that nice, how they named the signal something helpful and unambiguous? UART should take note with its transmit and receive that can be either inputs or outputs, depending on your point of view! Not cool, UART! Data driven from the master to the slave devices. Single Data Rate Clock with configurable edge polarity (rising or falling).

Driven by the SPI master and received by the SPI slave devices.

And, a clock signal is implemented for synchronous operation of the bus. One or more Chip Select (CS_L) signals is implemented to select a particular slave device in multi-slave configurations. Data is clocked out in serial form from master to slave on the MOSI line, and data is clocked in in serial form from slave to master on the MISO line. SPI is a serial bus and consists of a minimum of four signals. Electrical Engineering educational website

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. Archives

January 2023

Categories |

RSS Feed

RSS Feed